| Attachment | Size |

|---|---|

| 59.58 KB |

I just read UncleBernie's response here: https://www.applefritter.com/content/let-me-introduce-myself

So, I figured the timing was right to discuss the issue of SRAM write timing on an Apple II.

What I believe that UncleBernie is describing is a problem whereby if you synchronize the write with the fall of Phi2 that it is too late. The address and/or data is now corrupted, on the busses, and the data written will be bad. There is a similar problem, on Atari computers, due to the buffering of Phi2. I am also thinking the data bus corruption issue may be made worse because after Phi2 falls, the address and data busses are now used by the video subsystem so the additional hold time of the CPU is effectively eliminated.

I was looking into using SRAM and was thinking that it may be possible to use SRAM if the SRAM's write enable signal is high on read and low when the CPU R/W is low and /CAS is low. This would result in the SRAM write enable going high when /CAS goes high...which should result in the data being written before Phi2 falls and the busses are corrupted.

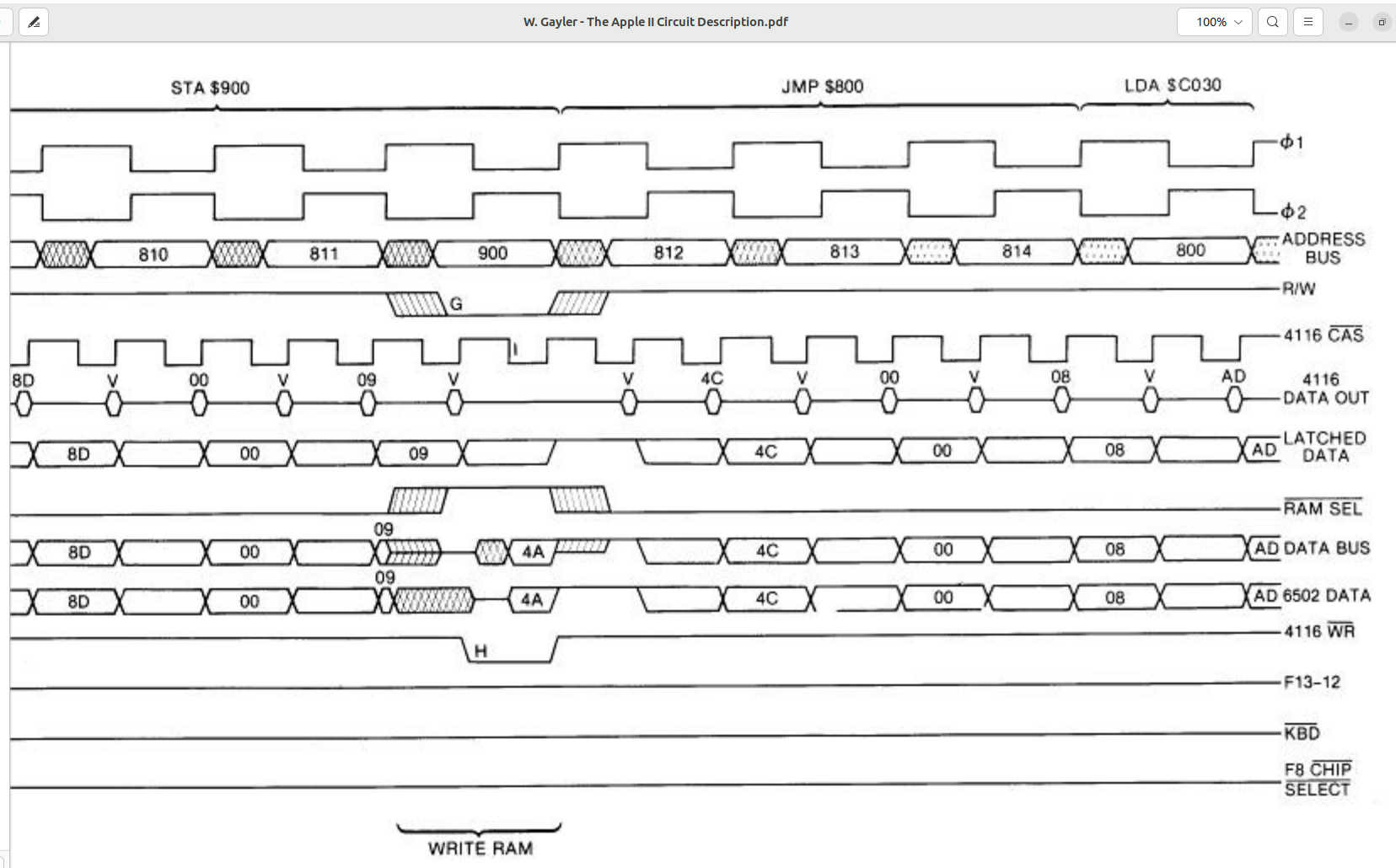

This chart shows why you wouldn't want to use Phi0 or Phi2 to synchronize the write timing:

While I didn't think about it, the soft switch latches should also be set using the same timing as writes to SRAM are set.

I was thinking it would be possible to use a PLD to build an apple II using SRAM like this:

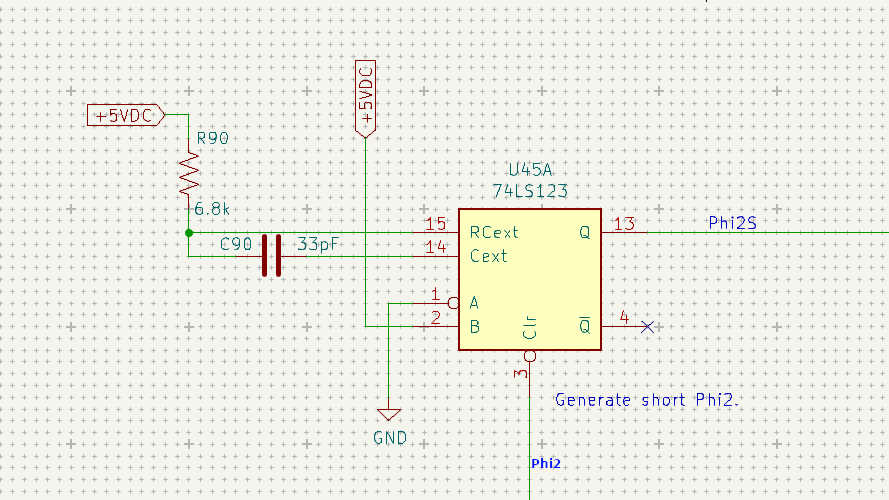

If using /CAS and RW for timing doesn't work, I think the next option would be to use a shortened Phi2 circuit like below and synchronize it with the write signal.

C90 and /or R90 may need some adjustment as this is used to time write signals on Atari PBI devices.

Thoughts?